# **Reconfigurable Multiprocessor System Reliability Estimation**

Oleg Viktorov

Department Software Engineering, Al-Zaytoonah University,

P.O. Box 1764, Amman, Jordan

**Abstract:** Reconfigurable multiprocessor systems offer an approach for improvement of system reliability. On the one hand the faults do not cause the whole system down because of the redundancy of such systems and suitable reconfiguration actions. From the other hand, higher system performance means more processors and other modules, which may result in more faults and a higher risk that system fails. Since classical reliability evaluation technique is not applicable to reconfigurable multiprocessor systems, another approach to reliability evaluation is presented. The result shows that the systems with multibus interconnection are the most reliable among all reconfigurable multiprocessor systems with bus oriented interconnection unit.

**Key words:**Reconfigurable multiprocessor systems, redundancy, single bus interconnection, multiple bus interconnection, multiport memory unit, cross-bar interconnection unit

#### INTRODUCTION

One of the most widely used way to increase system performance is a parallelism that is usually achieved by means of multiprocessing. However, this hardware overhead can be used also to increase system reliability. Conventional multiprocessor system consists of n processors  $P_1, P_2, \ldots, P_n$ , m memory units  $M_1, M_2, \ldots, M_m$  and interconnection unit. When a fault occurs system recovery should be done through reconfiguration of interconnection unit that consists of k switching elements  $S_1, S_2, \ldots, S_k$ . More then 10 interconnection unit structures are known (Selvaraj and Jozwiak, 2005; Ku and Hayes, 1997; Mahapatra and Dutt, 2001; Singh and Youn, 1991), but the investigations of system structures presented here is restricted to the following systems with bus oriented interconnection units:

- Common bus reconfigurable multiprocessor systems;

- Multibus reconfigurable multiprocessor systems;

- Multiport reconfigurable multiprocessor systems;

- Cross-bar reconfigurable multiprocessor systems.

Well-known formulas can be used for conventional multiprocessor system probability estimation (Kales, 1998). It seems that reconfigurable multiprocessor system reliability can be improved because their natural redundancy is used to increase reliability (Yu and Koren, 1994). So reconfigurable multiprocessor system reliability estimation is a new task and it needs some new approaches that have been presented in this study.

### REALIABILITY ESTIMATION APPROACH

A reconfigurable multiprocessor system has maximum configuration, if all n processors, m memory units, b interconnection buses and k switches are in full working order.

A reconfigurable multiprocessor system has minimum configuration, if a system has v nonfaulty units and single unit failure causes system down.

This reconfigurable multiprocessor systems reliability estimation approach uses D-the number of system configurations, in witch system is out of order.

$$D = (n-v+1)(n-v+1)/2$$

Common bus reconfigurable multiprocessor systems reliability can be defines by the following formula:

$$R(t) = 1 - \prod_{p=1}^{D} Q_{p}(t),$$

Where  $Q_p(t)$ -of the failure probability of the system in configuration p.

## RESULTS

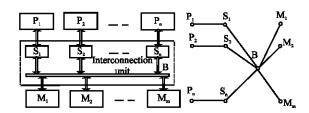

Common bus reconfigurable multiprocessor systems  $\mathbf{n}$  its graphical representation are shown in Fig.1 a and b. Common bus reconfigurable multiprocessor system reliability is:

Rcb (t) =

$$1 - \prod_{i=a}^{n} \prod_{j=b}^{m} \prod_{1=d}^{n} (1 - R_{P}^{i}(t) R_{m}^{j}(t) R_{B}(t) R_{S}^{1}(t)),$$

(1)

Fig. 1: Reconfigurable multiprocessor system with commen bus

### Where

- R<sub>p</sub><sup>i</sup>(t) is the probability that i-th processor performs the given function;

- R<sub>i</sub><sup>i</sup>(t) is the probability that j-th memory unit performs the given function;

- R<sub>B</sub>(t) is the probability that common bus provides the proper connection;

- R<sub>s</sub><sup>1</sup>(t) is the probability that 1-th switching element performs the given function.

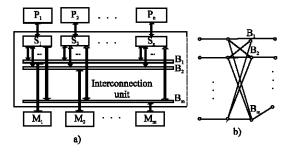

Multibus reconfigurable multiprocessor systems and its graphical representation are shown in Fig. 2a and b.

Multibus reconfigurable multiprocessor system reliability is:

$$\begin{split} R_{MB}(t) &= 1 \text{-} \prod_{i=a}^{n} \prod_{j=b}^{m} \prod_{k=c}^{m} \prod_{l=d}^{m} \text{ ,} \\ (1 \text{-} R_{p}^{i}(t) R_{m}^{j}(t) R_{B}^{k}(t) R_{S}^{l}(t)) \end{split} \tag{2}$$

### Where

- R<sub>p</sub><sup>i</sup>(t) is the probability that i-th processor performs the given function;

- R<sub>i</sub>(t) is the probability that j-th memory unit performs the given function;

- R<sub>B</sub><sup>k</sup>(t) is the probability that k-th common bus provides the proper connection;

- R<sub>s</sub><sup>1</sup>(t) is the probability that 1-th switching element performs the given function.

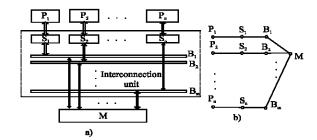

Multiport reconfigurable multiprocessor systems and its graphical representation are shown in Fig. 3 a and b.

Multiport reconfigurable multiprocessor system reliability is:

$$\begin{split} R_{\text{MPM}}(t) &= 1 \text{-} \prod_{l=c}^{n} \prod_{k=d}^{n} \prod_{k=c}^{m} \prod_{l=d}^{m} \\ & (1 \text{-} R_{\text{p}}^{i}(t) R_{\text{m}}^{i}(t) R_{\text{R}}^{k}(t) R_{\text{M}}(t)) \end{split} \tag{3}$$

#### Where

- R<sub>p</sub><sup>i</sup>(t) is the probability that i-th processor performs the given function;

- R<sub>B</sub>(t) is the probability that k-th common bus provides the proper connection;

Fig. 2: Reconfigurable multiprocessor system with multiple buses

Fig. 3: Reconfigurable multiprocessor system with multiple memory

- R<sub>s</sub><sup>1</sup>(t) is the probability that 1-th switching element performs the given function.

- R<sub>M</sub>(t) is the probability that multiport memory unit M performs the given function;

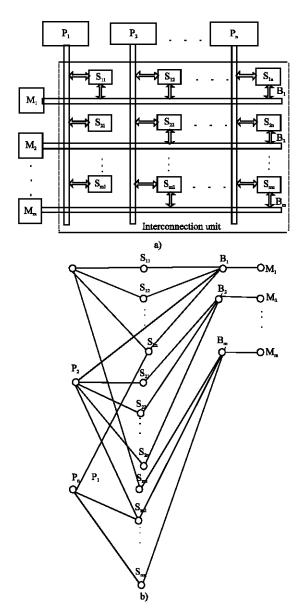

Cross-bar reconfigurable multiprocessor systems and its graphical representation are shown in Fig. 4 a and b.

Multibus reconfigurable multiprocessor system reliability is:

$$\begin{split} R_{cbs}(t) &= 1 \text{-} \prod_{l=c}^{n} \prod_{j=b}^{m} \prod_{k=c}^{m} \prod_{l=d}^{ixj} \\ & (1 \text{-} R_{v} R_{p}^{i}(t) R_{m}^{j}(t) R_{B}^{k}(t) R_{s}^{l}(t)) \end{split} \tag{4}$$

## Where

- R<sub>P</sub><sup>i</sup>(t) is the probability that i-th processor performs the given function;

- R<sub>i</sub>(t) is the probability that j-th memory unit performs the given function;

- R<sub>B</sub><sup>k</sup>(t) is the probability that k-th common bus provides the proper connection;

- R<sub>s</sub><sup>1</sup>(t) is the probability that 1-th switching element performs the given function.

$R_{\nu}$  is the probability that a multiprocessor system with v non faulty units performs assigned functions:

$$Rv = \sum_{i,i} \sum_{w} G/C_{i \times i}^{\max(i,j)}$$

Fig. 4: Reconfigurable cross-bar switch multiprocessor system

U is the set of partitions of max(i,j) on k addends; W is the set of matrices, which have no empty rows; G-the number of column arrangements for each matrices from the set W;

$C_{ixj}^{\max(i,j)}$ -the number of  $\max(i,j)$ -subsets of  $i \times j$  element set.

## CONCLUSION

Analysis of the expressions (1)-(4) and graphical representations (Fig. 1b-4b) shows that multibus reconfigurable multiprocessor system has the highest system reliability, because maximum and minimum configurations common bus reconfigurable of systems multiprocessor (multiport reconfigurable multiprocessor systems) are the same (Fig 1b-3b). The complexity of cross-bar reconfigurable multiprocessor systems grows gradually ( O(N2) ) with number of processors and memory units, that definitely badly affects the system reliability.

#### REFERENCES

- Kales, P., 1998. Reliability for Technology, Engineering and Management, Prentice Hall.

- Ku Hung-Kuei and J. Hayes, 1997. Systematic Design of Fault-Tolerant Multiprocessor with Shared Buses, IEEE Trans. Computers, 46: 439-445.

- Mahapatra, N.R. and S. Dutt, 2001. Hardware-efficient and Highly Reconfigurable 4-and 2-track Fault-tolerant Designs for Mesh-connected Arrays, J. Parallel and Distributed Compu., 61: 1391-1411.

- Selvaraj, H. and L. Jozwiak, 2005. Reconfigurable Embedded Systems: Synthesis, Design and Application, J. Sys. Architecture, 51: 347-349.

- Singh, A.D. and H.Y. Youn, 1991. A Modular Faulttolerant Binary Tree Architecture with Short Links, IEEE Trans. Computers, 40: 882-890.

- Yu Kai and I. Koren, 1994. Reliability Enhancement of Real-time Multiprocessor Systems through Dynamic Reconfiguration, Fault-tolerant Parallel and Distributed Systems, Proceeding of IEEE, Workshop, pp: 161-168.